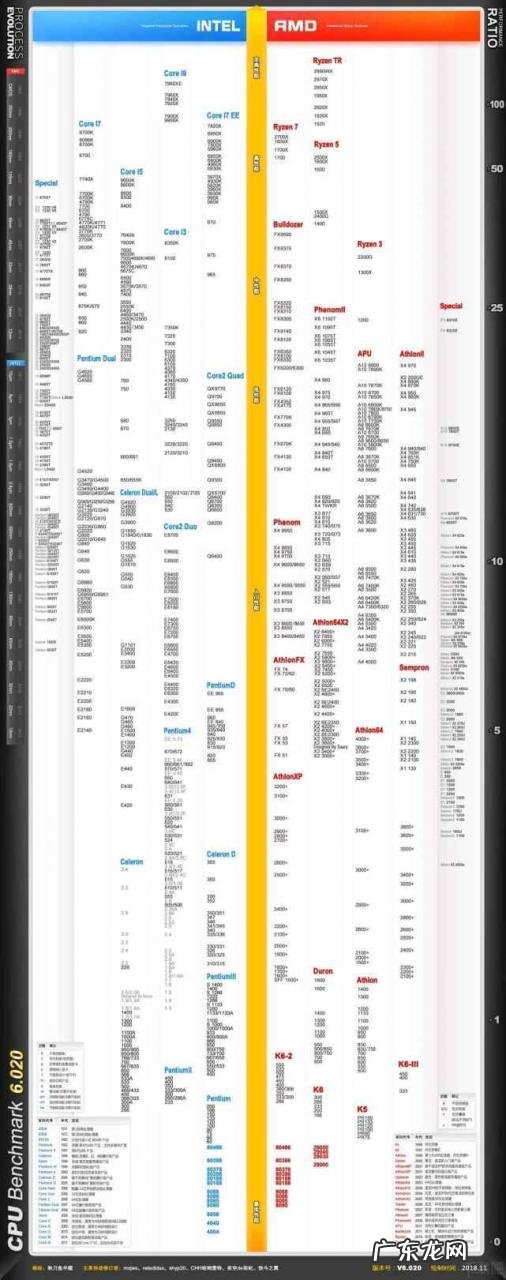

7.CPU扩展指令集

CPU依靠指令来计算和控制系统, 每款CPU在设计时就规定了一系列与其硬件电路相配合的指令系统 。 指令的强弱也是CPU的重要指标, 指令集是提高微处理器效率的最有效工具之一 。 从现阶段的主流体系结构讲, 指令集可分为复杂指令集和精简指令集两部分, 而从具体运用看, 如Intel的MMX(Multi Media Extended)、SSE、 SSE2(Streaming-Single instruction multiple data-Extensions 2)、SEE3和AMD的3DNow!等都是CPU的扩展指令集, 分别增强了CPU的多媒体、图形图象和Internet等的处理能力 。 我们通常会把CPU的扩展指令集称为”CPU的指令集” 。 SSE3指令集也是目前规模最小的指令集, 此前MMX包含有57条命令, SSE包含有50条命令, SSE2包含有144条命令, SSE3包含有13条命令 。 目前SSE3也是最先进的指令集, 英特尔Prescott处理器已经支持SSE3指令集, AMD会在未来双核心处理器当中加入对SSE3指令集的支持, 全美达的处理器也将支持这一指令集 。 主频

文章插图

CPU各项参数及其用途CPU参数一级缓存和二级缓存的作用!!

一级缓存:

高速缓存分为一级缓存(即L1 Cache)和二级缓存(即L2Cache) 。 CPU在运行时首先从一级缓存读取数据, 然后从二级缓存读取数据, 然后从内存和虚拟内存读取数据, 因此高速缓存的容量和速度直接影响到CPU的工作性能 。

那么, 二级缓存的作用又是什么呢?简单地说, 二级缓存就是一级缓存的缓冲器:一级缓存制造成本很高因此它的容量有限, 二级缓存的作用就是存储那些CPU处理时需要用到、一级缓存又无法存储的数据 。 同样道理, 三级缓存和内存可以看作是二级缓存的缓冲器, 它们的容量递增, 但单位制造成本却递减 。 需要注意的是, 无论是二级缓存、三级缓存还是内存都不能存储处理器操作的原始指令, 这些指令只能存储在CPU的一级指令缓存中, 而余下的二级缓存、三级缓存和内存仅用于存储CPU所需数据 。

AMD一级数据缓存设计

AMD采用的一级缓存设计属于传统的“实数据读写缓存”设计 。 基于该架构的一级数据缓存主要用于存储CPU最先读取的数据;而更多的读取数据则分别存储在二级缓存和系统内存当中 。 做个简单的假设, 假如处理器需要读取“AMD ATHLON 64 3000+ IS GOOD”这一串数据(不记空格), 那么首先要被读取的“AMDATHL”将被存储在一级数据缓存中, 而余下的“ON643000+ISGOOD”则被分别存储在二级缓存和系统内存当中(如下图所示) 。

需要注意的是, 以上假设只是对AMD处理器一级数据缓存的一个抽象描述, 一级数据缓存和二级缓存所能存储的数据长度完全由缓存容量的大小决定, 而绝非以上假设中的几个字节 。 “实数据读写缓存”的优点是数据读取直接快速, 但这也需要一级数据缓存具有一定的容量, 增加了处理器的制造难度(一级数据缓存的单位制造成本较二级缓存高) 。

二、Intel一级数据缓存设计

自P4时代开始, Intel开始采用全新的“数据代码指令追踪缓存”设计 。 基于这种架构的一级数据缓存不再存储实际的数据, 而是存储这些数据在二级缓存中的指令代码(即数据在二级缓存中存储的起始地址) 。 假设处理器需要读取“INTEL P4 IS GOOD”这一串数据(不记空格), 那么所有数据将被存储在二级缓存中, 而一级数据代码指令追踪缓存需要存储的仅仅是上述数据的起始地址() 。 cpu缓存(cache memory)位于cpu与内存之间的临时存储器, 它的容量比内存小但交换速度快 。 在缓存中的数据是内存中的一小部分, 但这一小部分是短时间内cpu即将访问的, 当cpu调用大量数据时, 就可避开内存直接从缓存中调用, 从而加快读取速度 。 由此可见, 在cpu中加入缓存是一种高效的解决方案, 这样整个内存储器(缓存+内存)就变成了既有缓存的高速度, 又有内存的大容量的存储系统了 。 缓存对cpu的性能影响很大, 主要是因为cpu的数据交换顺序和cpu与缓存间的带宽引起的 。

特别声明:本站内容均来自网友提供或互联网,仅供参考,请勿用于商业和其他非法用途。如果侵犯了您的权益请与我们联系,我们将在24小时内删除。